上周受英特尔邀请,我参加了在上海举办的“英特尔先进封装技术解析会”,因为这次会议来的都是英特尔封装技术部门的专家,所以这是一场干货十足、充满硬核技术的解析会。

我们先来看一段英特尔的官方讲解视频:

这次参会的过程就像是上了一堂技术大课,超级烧脑,也让我对英特尔封装技术有了更为深入和直观的了解。虽然我对技术不太懂,但我可以把了解到的东西梳理成文,所以接下来,我试着把英特尔技术专家们谈及的技术点,用相对系统化的方式传达给大家。

·了解封装

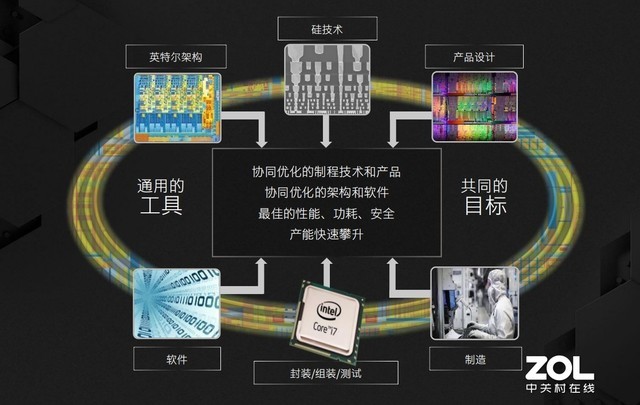

封装技术是半导体行业的支柱性技术,英特尔在去年发布的六大技术支柱里(制程和封装,架构,内存和存储,互连,安全,软件),封装赫然在列,并且可以说是其它几大支柱的根基。所以封装对于英特尔来说是极其重要的核心技术。

英特尔六大技术支柱

英特尔制程及封装部门技术营销总监Jason Gorss表示,“之所以把制程&封装放在最下面,因为它可以说是上面五大支柱的重要核心,也是我们最基础的一个要素。在制程和封装领域我们要做的创新集中在晶体管和封装两大领域,晶体管层面我们希望未来尺寸会越来越小,并且功耗越来越下降,这是我们晶体管领域主要的创新方向。”

此外不吹不黑的是,英特尔是目前这个星球上唯一的、同时能够实施这六大技术战略的半导体公司。

英特尔作为一家IDM(垂直集成厂商)所具备的优势

·了解英特尔的先进封装技术

去年,英特尔推出了冥王峡谷NUC,搭载了一颗颇为独特的处理器:酷睿i7 8809G。这颗处理器的独特之处在于,其GPU部分搭载了AMD Radeon RX Vega M GH Graphics集成显卡。

英特尔冥王峡谷NUC采用了EMIB封装技术打造的酷睿i7 8809G处理器

英特尔的处理器配上AMD的集成显卡?这是什么神仙操作?

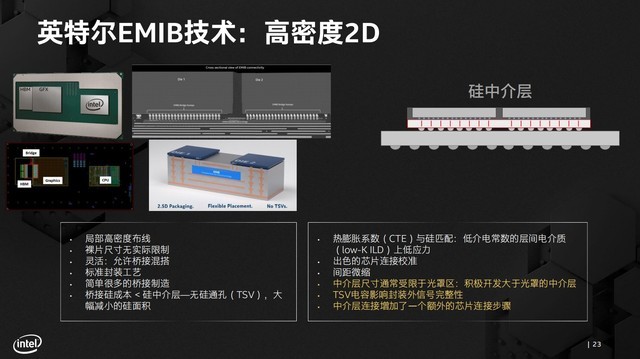

原来,英特尔酷睿i7 8809G采用了一种名为EMIB的2D封装技术,通过嵌入式桥接将英特尔的CPU和AMD的GPU封装在一个芯片上,综合了英特尔处理器的优秀计算能力,以及AMD GPU的出色图形性能。这可以说是英特尔先进封装技术的首秀。

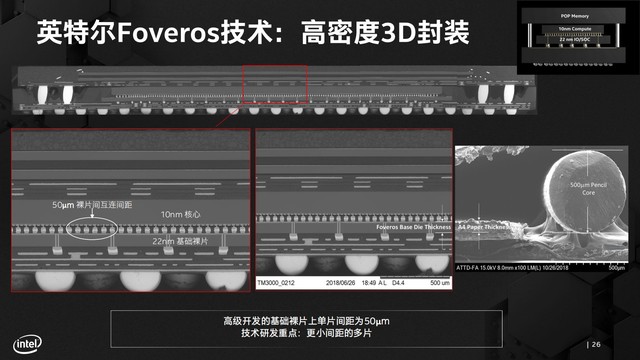

此后,英特尔再接再厉,在今年初CES上公布了Foveros 3D封装技术,并展示了首款3D堆叠芯片Lake Field。3D封装技术使其能够在芯片之上继续实现堆叠封装,可以有效缩小芯片体积。

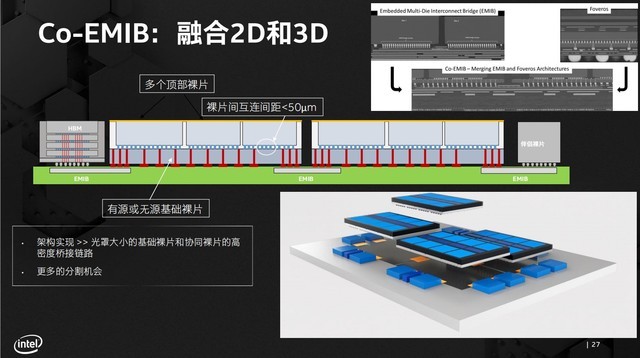

再之后,英特尔又推出了融合EMIB和Foveros封装技术的Co-EMIB,将2D封装和3D封装进行了有机结合,实现了上下左右各个方位的芯片堆叠封装。

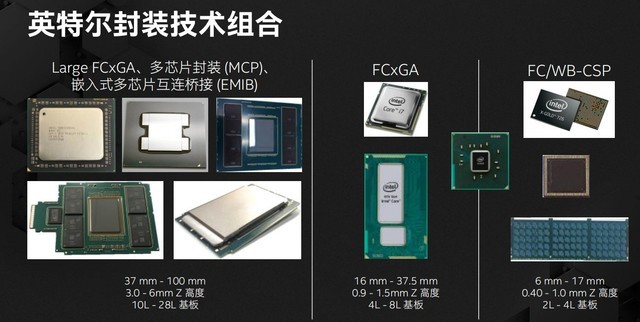

·目前英特尔有哪些先进封装技术?

说到这里,可能大家会产生一个疑问,一直在说先进封装技术,那么英特尔到底有哪些先进封装技术呢?

其一, EMIB,也就是之前提到的酷睿i7 8809G处理器用到的技术。它是高密度2D封装技术,也就是在平面上做高密度封装,这种封装技术的重点在于能够将做到多薄,再者是多个裸片之间的间距到底是多少。

EMIB很像盖平房,在一块地上盖上不同样式风格的小房子,并且用路把它们连接起来。

其二,Foveros,也就是之前提到的Lake Field所使用的高密度3D封装技术。Foveros也是盖房子,但更像是盖楼房。

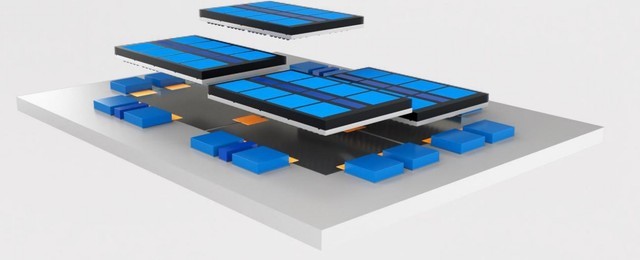

其三,Co-EMIB,简单来说就是EMIB与Foveros的结合,融合了2D封装和3D封装技术的优势。Co-EMIB可以把超过两个以上的不同裸片来进行叠加,并可以在水平和垂直方向实现叠加,具备更好的灵活度。

2D和3D其实很好理解,2D就是平面封装,芯片上面不会再有其它芯片;而3D则是在芯片上继续堆叠芯片。

轻松看懂Co-EMIB封装

·为啥要搞封装技术?

过去,我们所理解的封装,就是把Die封装到基板上做成CPU。但是英特尔先进封装技术却不仅仅如此,因为它可以实现不同制程、不同规格芯片的封装。那么意义在哪里呢?

我们都知道,一颗处理器芯片里其实不仅仅只有计算核心,同时还包含诸多的I/O部分。以往的封装是把同制程工艺的芯片封装在一起,但事实上,CPU部分是需要先进制程工艺的,但I/O部分往往并不需要那么先进的制程工艺。比如现在的CPU是10nm,但I/O部分可能用14nm或22nm制程就能解决问题了,而且可以获得相当好的良率,但以往的封装技术只能将I/O部分也做成10nm,简直是劳民伤财。

英特尔这些先进封装技术就是为了解决这种问题而来的。通过将不同制程工艺的大小核封装在一个芯片上,就可以变得更加灵活,不需要10nm制程工艺打造的芯片,就可以用更加成熟、成本更低的14nm或22nm制程来打造,这是英特尔大力发展封装技术的动力所在。

英特尔封装技术可以灵活运用

此外,2D或3D封装还可以实现不同功能芯片之间的组合,比如Ice Lake做大核心保证计算性能,超低功耗的Atom做小核心来处理一些基础应用;再比如之前提到的酷睿i7 8809G,英特尔的处理器做计算,AMD的显卡做图形渲染,类似这样的例子,都能通过封装技术轻松实现。

·封装技术流程

那么,英特尔封装技术的实现流程是怎样的呢?来看下面这张图:

从左向右,首先英特尔将硅晶圆制造出来并对其进行晶圆级测试,选择究竟是哪一种芯片会更适合这个单独的晶圆。

接下来会进行硅片处理,也就是把晶圆分割成更加小的一些裸片。如果想像不到的话,把你的CPU盖撬开,然后就能看到一块很漂亮的、亮面的物体,把那个抠下来就是裸片了。

下一步,英特尔KGD(已知合格芯片)部门会确保提交给客户的所有芯片都是质量合格的。在这里,英特尔会通过连接到裸片上的具体接口以及插口对裸片进行测试,对其合格率进行分析认证。

完成这一步之后,接下来就进入封装阶段,简而言之就是把合格的裸片与基板和其它封装材料共同封装在一起。

完成封装后,英特尔会对其进行统一测试,确保它们可以正常运作。而在完成阶段,英特尔会确保整个芯片包括封装都会正常运行,接下来就是把这些封装测试好的合格芯片交付给客户。另外在彻底结束之前,英特尔会通过非常完整的表面贴装技术开发产品线来确保所有的封装在正式交付客户之前都经过完整的组装以及测试。

SMT开发线简介

这就是半导体芯片从晶圆到裸片,再到封装、到测试,最后到交付的完整过程。

·先进的多芯片封装架构(MCP)

对英特尔来说,在封装领域有一个愿景,即开发和拥有领先技术,能够在一个封装内连接芯片和小芯片,实现单晶片系统芯片(SoC)的功能。而实现低功耗高带宽的高密度互连,对于实现这个愿景至关重要。

英特尔院士兼技术开发部联合总监Ravindranath (Ravi) V. Mahajan说:“英特尔封装其实非常简单,就是可以把多个功能内部在封装内实现芯片和小芯片的连接,同时也可以帮助我们的整体芯片实现单晶片系统和片上系统的功能。为了做到这一点,我们必须要确保的是在整个裸片上的小芯片连接必须是低功耗、高带宽而且是高性能的。这也是我们实现这一愿景的重要核心。”

在这一方面,英特尔确立了三大技术开发目标:低延时、高互连速度以及高性能。

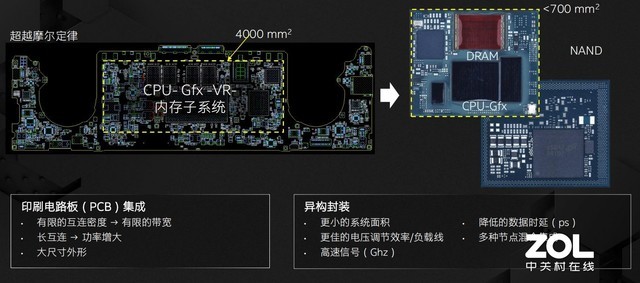

为了做到这一点,所有的封装都非常非常小,且必须要做到足够轻薄、足够小巧。但在整个封装内部,不同元件信号传递必须要是非常高速的。以下图所示为例:

这是英特尔将一块4000平方毫米的主板(包括CPU、GPU、存储器、电压调节器、内存子系统),通过先进封装技术整合到一块小于700平方毫米的基板之上,芯片体积显著缩小,物理距离缩减,使元件之间的信号传输速度有效提升,并实现了低时延以及更好的电压调节效率。

英特尔封装技术之所以先进,是因为它还支持多种节点混合集成,实现多个不同元器件的集成,尺寸会继续缩减。而这种缩减不仅仅是X轴和Y轴的平面缩减,更可以通过3D封装技术延伸的G轴,也就是高度上的缩减。

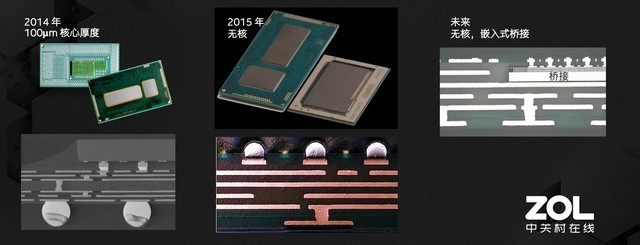

2014年,英特尔封装的PCB板厚度在100微米左右,2015年实现的无核技术封装使得基板厚度进一步缩减,而未来通过嵌入式桥接,英特尔不仅仅可以把硅片叠到封装上,还可以直接把硅片放在封装里面,这样就可以让芯片尺寸变得更加小巧。

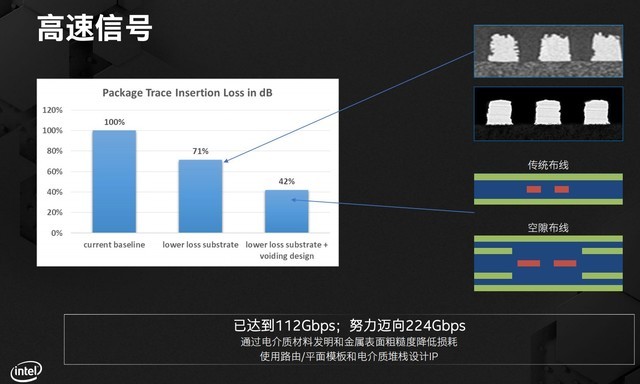

芯片封装体积缩小,最为直接的好处是可以实现信号传输的物理距离缩短,提升信号传输速度。此外,英特尔在电介质材料发明方面也有所突破,并通过专门的制造技术让金属表面粗糙度得到大幅降低,另外采用全新的布线方法减少串扰,多种方式实现信号高速传输。目前,英特尔通过先进封装技术已经可以达到112Gbps的传输速率,而未来的目标则是达到224Gbps的数量级。

图片右侧蓝色区域为电介质材料

·先进的IO技术

既然谈到封装技术,那么就避不开IO相关话题。

无论是EMIB还是Foveros,亦或是结合二者之长的Co-EMIB技术,都是将芯片进行封装的技术,但是仅仅把芯片进行封装是没法工作的,这时就需要IO技术来联通各个裸片。所以,先进的IO技术在封装范畴是相当核心的技术点。

英特尔此前公布了两种领先的IO技术:AIB(高级接口总线)和MDIO(多裸片间接口技术)。后者可以看作是前者的升级版,支持对小芯片IP模块库的模块化系统设计,可以在整个封装内实现裸片间互连,提供更高能效,实现AIB技术两倍以上的响应速度和带宽密度。

此外,台积电此前也公布了其IO技术LIPINCON,相对比之下可以发现,LIPINCON虽然在针脚速度方面有所领先,但MDIO在带宽密度上更加高效。

总体来说,对高带宽、低功耗IO链路的需求,推动了对先进多芯片封装 (MCP)架构的关注,EMIB、Foveros和Co-EMIB则是构建高密度MCP的关键基础技术。此外,英特尔通过MDIO和AIB这些领先的IO技术,并利用高密度MCP技术组合来进行协同设计,这些技术共同为英特尔提供了向上和向外扩展异构计算元素的架构和功能。

·先进的封装互连技术

封装与互连,是不可分割的关键技术。英特尔在封装领域的研究过程中,对互连技术的研究也在同步进行。

现阶段,封装互连技术有两种主要的方式:

其一,把主要的相关功能在封装上进行集成。比如把电压调节单元从母板移到封装上,通过这种方式实现全面集成的电压调节封装。

其二,是SoC片上系统分解方式的封装互连。把具备不同功能属性的小芯片来进行连接,并放在同一封装里,通过这种方法可以实现接近于单晶片的性能和功能。

同时,不论是哪一种实现路径,都需要英特尔做到异构集成和专门的带宽需求,而异构集成和专门的带宽需求也可以帮助英特尔实现密度更高的多芯片集成。

提到封装互连就不得不说微缩。

时下,英特尔微缩技术有三种方向:

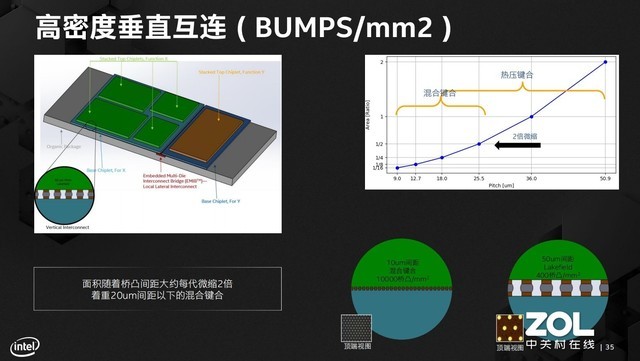

其一,高密度垂直互连,用于堆叠裸片。可以大幅度提高带宽,同时也可以实现高密度裸片叠加。高密度垂直互连使裸片间距变得越来越小,信号传导距离变得越来越短,从而促使信号传导速度更快,时间更短,中间的串扰更少。有效降低时延,提高信号速率。同时因为裸片间距越来越窄,电容和电压更低,可以大幅度降低功耗。

高密度垂直互连示意

其二,全局横向互连,实现大面积拼接。随着小芯片使用越来越普及,英特尔希望在小芯片集成当中保证更高的带宽。英特尔使用每毫米引线数量来衡量,而使用全局横向互连可以做到整个封装层面的小芯片互连。

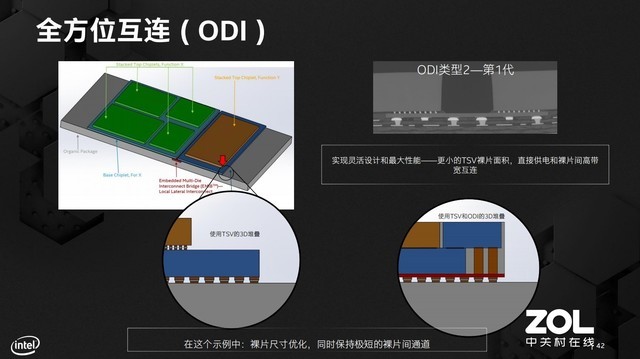

其三,全方位互连,主要意义在于提升性能,也就是前不久英特尔公布的ODI。通过全方位互连可以实现之前所无法达到的3D堆叠带来的性能提升。

全方位互连(ODI)示意

常规叠加方式下,基础裸片体积必须要更大一些,往往要大于上面叠加的所有小芯片的总和。而ODI技术则可以改变这一点,使大小芯片之间可以进行更好的协调,并且可以做到上下面积统一。

ODI技术拥有三大优势:

第一,保证上方裸片和下方基础裸片之间的带宽速度足够快。

第二,上面的小芯片可以直接获得封装供电,而并不需要中间通孔方式来获得,可以带来供电优势。

第三,通过全方位互连(ODI)技术,基础裸片就不用像过去那样一定要比上方叠加的小芯片的面积总和更大。

·TIPS:混合键合,全新的焊料技术

到这里我们可以总结出一些要点,封装技术的关键指标在于封装之后各芯片间的互连,而互连需要解决带宽问题和信号传输问题。随着摩尔定律继续推进,芯片尺寸变得越来越小,为了保证足够带宽,就必须要在导线上下功夫,也就是要在微缩上实现新的突破,这是英特尔推进封装技术过程中绕不过的坎儿。

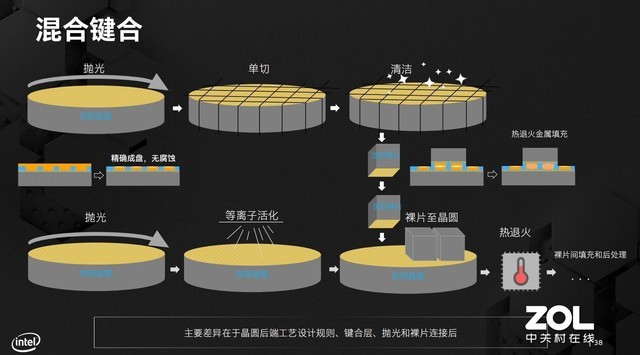

目前,芯片封装间距越来越短,传统焊料技术已经趋于极限,为了保证带宽,必须要有新的方案来保证未来的发展,名为“混合键合”的技术应运而生,它是一种非焊料的焊接技术。通过混合键合的方法,英特尔在间距上可以做到10微米,除此之外在桥凸和互连密度上都可以做到更好。

混合键合技术

多芯片封装架构(MCP)、封装技术(EMIB、Foveros、Co-EMIB),再加上先进的IO技术(AIB、MDIO)以及全方位互连(ODI)技术,英特尔在封装领域已经取得了极大突破。

对于现有架构,英特尔MCP架构通过混合键合技术实现非常高密度的垂直互连,通过无未对准通孔(ZMV)技术可以更好实现高密度互连。通过这些全新的架构和技术,英特尔可以把垂直互连和全横向互连的最大优势都实现出来。

此外,在技术路线方面,除了现在已经实现的Co-EMIB之外,英特尔未来还考虑将ZMV和Foveros集成,或者EMIB与ZMV集成。

·先进封装技术的实际应用意义

写到这里,可能有人会问,这些技术的实际应用意义在哪?

其实,技术都是底层的东西,对于用户来说没有直接关系,但却不可忽视技术对世界的改变。就英特尔封装技术而言,它可以为不同需求的用户灵活组建不同功能的芯片,可以有效的、灵活的控制芯片成本,可以抛开制程对芯片发展带来的掣肘,避免过度依赖制程提升带来的性能提升,可以为PC半导体芯片的发展开拓出一条新的道路。

看此文章的还看过:《方寸之地别有洞天 揭开英特尔封装技术面纱》由笔记本电脑排行榜原创提供,转载请注明:https://www.fzmo.cn/html/1470.html